- 您现在的位置:买卖IC网 > Sheet目录479 > MRF49XAT-I/ST (Microchip Technology)IC RF TXRX 433/868/915 16-TSSOP

MRF49XA

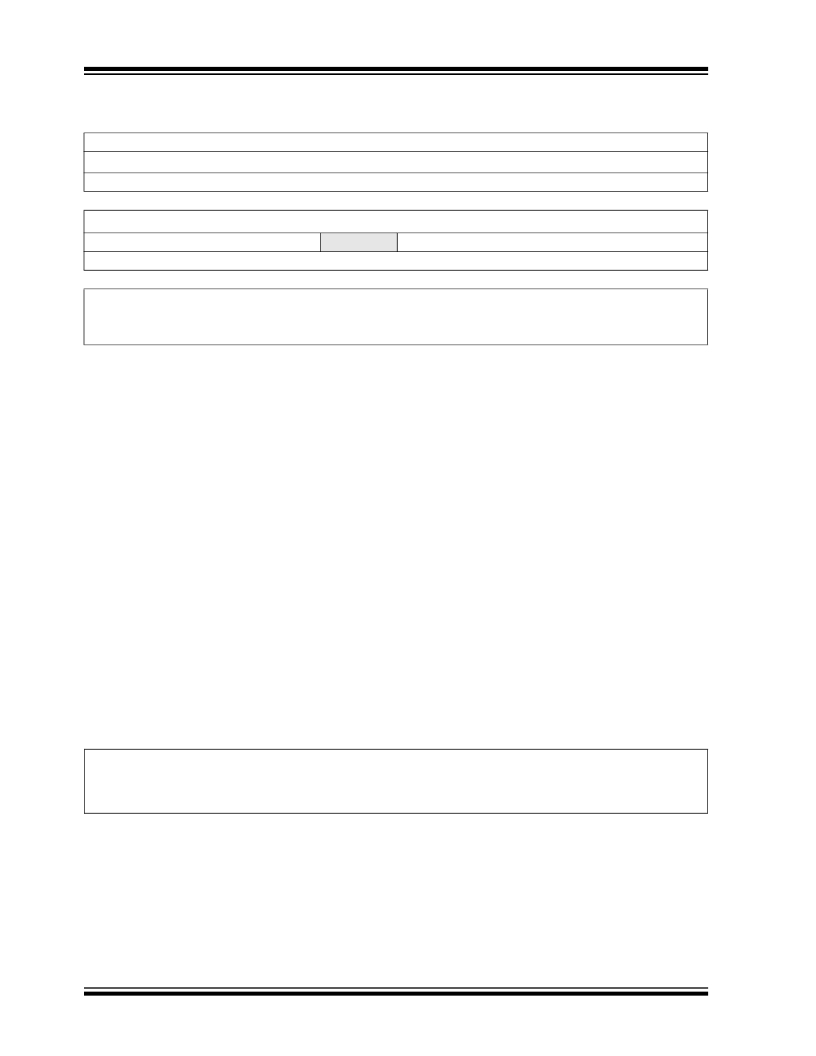

REGISTER 2-16:

BCSREG: BATTERY THRESHOLD DETECT AND CLOCK OUTPUT VALUE SET

REGISTER (POR: 0xC000)

W-1

W-1

W-0

W-0

W-0

W-0

W-0

W-0

CCB<15:8>

bit 15

bit 8

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

COFSB<2:0>

r

LBDVB<3:0>

bit 7

Legend:

r = reserved bit

bit 0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 15-8

bit 7-5

bit 4

bit 3-0

Note 1:

2:

CCB<15:8>: Command Code bits

The command code bits ( 11000000b ) are serially sent to the microcontroller to identify the bits to be

written in the BCSREG.

COFSB<2:0>: Clock Output Frequency Set bits

These bits set the output clock frequency which can be used to run an external host microcontroller.

111 = 10 MHz

110 = 5 MHz

101 = 3.33 MHz

100 = 2.5 MHz

011 = 2 MHz

010 = 1.66 MHz

001 = 1.25 MHz

000 = 1 MHz

Reserved: Write as ‘ 0 ’

LBDVB<3:0>: Low Battery Detect Value bits

These bits set the decimal value to calculate the battery detect threshold voltage level (1,2) .

When the battery level goes down by 50 mV below this value, the LBTD bit (STSREG<10>) is set, indicating

that the battery level is below the programmed threshold. This is useful in monitoring discharge-sensitive

batteries, such as Lithium cells. The low battery detect can be enabled by setting the LBDEN bit

(PMCREG<2>) and can be disabled by clearing the bit.

The low battery threshold value is programmable from 2.2V – 3.8V by using Equation 2-9 .

EQUATION 2-9:

Threshold Voltage Value = 2.25 +[0.1 x (LBDVB<3:0>)]

where:

LBDVB<3:0> is the Decimal Value from 0 to 15.

DS70590C-page 40

Preliminary

? 2009-2011 Microchip Technology Inc.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MRF89XA-I/MQ

TXRX ISM SUB-GHZ ULP 32QFN

MRF89XAM9A-I/RM

IC TXRX MOD 915MHZ ULP SUB-GHZ

MRX-001-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002SL-433DR-B

MODULE RCVR 433MHZ SAW LN 24DIP

MRX-005-915DR-B

MODULE RECEIVER 915MHZ 18DIP

MRX-005SL-915DR-B

MODULE RCVR 915MHZ SAW LN 24DIP

MRX-007-433DR-B

MODULE RECEIVER 433MHZ 18DIP

相关代理商/技术参数

MRF49XAT-I/T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-ST

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF4A(AMMO)

制造商:Bel Fuse 功能描述:FUSE

MRF5

制造商:Ferraz Shawmut 功能描述:

MRF50

制造商:Ferraz Shawmut 功能描述:

MRF500

制造商:Ferraz Shawmut 功能描述:

MRF5003

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:N-CHANNEL BROADBAND RF POWER FET